Page 104 - 无损检测2025年第二期

P. 104

郭蔚潇,等:

基于阈值欠采样的数字式涡流检测系统

益。为保证输出信号的载荷能力,防止输出正弦波

畸变,文章基于THS3 091低失真电流反馈运放芯片

设计二级放大电路,并固定2倍增益,确保信号达到

系统所需幅度范围的同时,信噪比也得到提高。

2.3 检测电路

检测电路系统框图如图3所示,是一种由检测

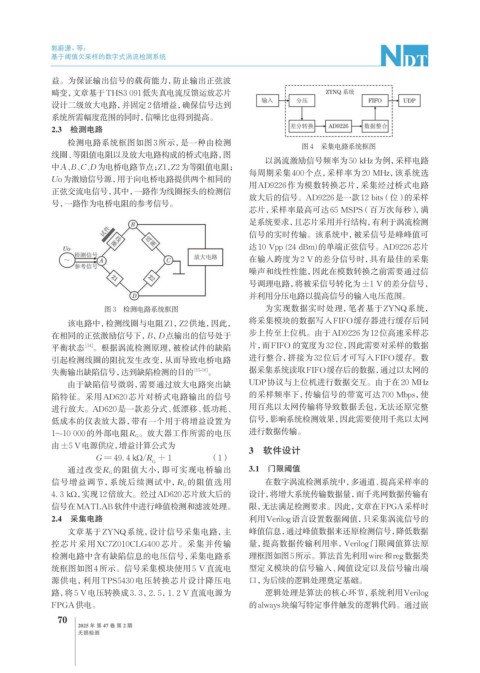

图 4 采集电路系统框图

线圈、等阻值电阻以及放大电路构成的桥式电路,图

以涡流激励信号频率为50 kHz为例,采样电路

中A、 B、 C、 D为电桥电路节点;Z1,Z2为等阻值电阻;

每周期采集400个点,采样率为20 MHz,该系统选

Uo为激励信号源,用于向电桥电路提供两个相同的

用AD9226作为模数转换芯片,采集经过桥式电路

正弦交流电信号,其中,一路作为线圈探头的检测信

放大后的信号。AD9226是一款12 bits (位)的采样

号,一路作为电桥电阻的参考信号。

芯片,采样率最高可达65 MSPS (百万次每秒),满

足系统要求,且芯片采用并行结构,有利于涡流检测

信号的实时传输。该系统中,被采信号是峰峰值可

达10 Vpp (24 dBm)的单端正弦信号。AD9226芯片

在输入跨度为2 V的差分信号时,具有最佳的采集

噪声和线性性能,因此在模数转换之前需要通过信

号调理电路,将被采信号转化为±1 V的差分信号,

并利用分压电路以提高信号的输入电压范围。

图 3 检测电路系统框图 为实现数据实时处理,笔者基于ZYNQ系统,

该电路中,检测线圈与电阻Z1,Z2供地,因此, 将采集模块的数据写入FIFO缓存器进行缓存后同

在相同的正弦激励信号下, B, D点输出的信号处于 步上传至上位机。由于AD9226为12位高速采样芯

平衡状态 [14] 。根据涡流检测原理,被检试件的缺陷 片,而FIFO 的宽度为32位,因此需要对采样的数据

引起检测线圈的阻抗发生改变,从而导致电桥电路 进行整合,拼接为32位后才可写入FIFO缓存。数

失衡输出缺陷信号,达到缺陷检测的目的 [15-16] 。 据采集系统读取FIFO缓存后的数据,通过以太网的

由于缺陷信号微弱,需要通过放大电路突出缺 UDP协议与上位机进行数据交互。由于在20 MHz

陷特征。采用AD620 芯片对桥式电路输出的信号 的采样频率下,传输信号的带宽可达700 Mbps,使

进行放大。AD620是一款差分式、低漂移、低功耗、 用百兆以太网传输将导致数据丢包,无法还原完整

低成本的仪表放大器,带有一个用于将增益设置为 信号,影响系统检测效果,因此需要使用千兆以太网

1~10 000的外部电阻R G 。放大器工作所需的电压 进行数据传输。

由±5 V电源供应, 增益计算公式为

3 软件设计

G = 49. 4 kΩ/R + 1 (1)

G

通过改变R G 的阻值大小,即可实现电桥输出 3.1 门限阈值

信号增益调节,系统后续测试中, R G 的阻值选用 在数字涡流检测系统中,多通道、提高采样率的

4. 3 kΩ,实现12倍放大。经过AD620芯片放大后的 设计,将增大系统传输数据量,而千兆网数据传输有

信号在MATLAB软件中进行峰值检测和滤波处理。 限,无法满足检测要求。因此,文章在FPGA采样时

2.4 采集电路 利用Verilog语言设置数据阈值,只采集涡流信号的

文章基于 ZYNQ系统,设计信号采集电路,主 峰值信息,通过峰值数据来还原检测信号,降低数据

控芯片采用 XC7Z010CLG400 芯片。采集并传输 量,提高数据传输利用率,Verilog门限阈值算法原

检测电路中含有缺陷信息的电压信号,采集电路系 理框图如图5所示。算法首先利用wire和reg数据类

统框图如图 4 所示。信号采集模块使用5 V直流电 型定义模块的信号输入、阈值设定以及信号输出端

源供电,利用 TPS5430 电压转换芯片设计降压电 口,为后续的逻辑处理奠定基础。

路,将5 V电压转换成3. 3,2. 5,1. 2 V直流电源为 逻辑处理是算法的核心环节,系统利用Verilog

FPGA供电。 的always块编写特定事件触发的逻辑代码。通过嵌

70

2025 年 第 47 卷 第 2 期

无损检测