# 超声相控阵检测硬件电路设计

王海涛<sup>1</sup>, 葛金鑫<sup>1</sup>, 杨先明<sup>2</sup>

(1. 南京航空航天大学 自动化学院,南京 210016; 2. 烟台富润实业有限公司,烟台 264670)

**摘要:**相控阵超声成像检测技术在工业无损检测领域中的应用越来越广泛。其通过控制阵列探头中各个阵元激励脉冲的时间延迟,以实现聚焦点位置和声束方位的变化,从而合成相控阵波束,完成超声扫描成像。设计了超声发射接收电路,并通过超声标准试块验证单通道超声检测电路的可行性。根据设计要求,将单通道电路进行相应的扩展,可得到多通道相控阵超声检测电路并通过控制现场可编程门阵列(FPGA)实现检测。

**关键词:**相控阵超声成像;发射电路;信号处理电路;试块检测

中图分类号:TG115.28; TN911.7 文献标志码:A 文章编号:1000-6656(2014)05-0019-04

## The Design of Ultrasonic Phased Array Testing Hardware Circuit

WANG Hai-tao<sup>1</sup>, GE Jin-xin<sup>1</sup>, YANG Xian-ming<sup>2</sup>

(1. School of Automation Engineering, Nanjing University of Aeronautics and Astronautics, Nanjing 210016, China;

2. Yantai Furun Industrial Company with Limited Liability, Yantai 264670, China)

**Abstract:** Nowadays the ultrasonic phased array imaging detection technology has an increasingly wide application in the field of industrial non-destructive testing. By controlling the delay time of each element, the technology can change the location of the focus point and the direction of the beam and therefore form combined phased beam, complete ultrasonic scanning imaging. This paper studies the design of ultrasonic transmit-receive circuit. And use ultrasound test block is used to verify the feasibility of the single-channel ultrasonic testing circuit. The actual phased array ultrasonic detection circuit is a repeated combination of the single-channel circuit and the FPGA is then used to achieve detection.

**Keywords:** Ultrasonic phased array imaging; Transmitting circuit; Signal processing circuit; Block detection

目前,相控阵超声成像检测技术在工业无损检测领域中的应用越来越广泛。相控阵超声成像检测技术是采用多阵元阵列换能器,依靠计算机技术控制阵列中各阵元发射超声波的时间(相位)来控制各阵元的声束在声场中的偏转、聚焦;或控制接收阵列换能器中各阵元接收回波信号的时间(相位),进行偏转、聚焦成像检测的一种高端技术,是目前超声检测技术中的发展热点之一<sup>[1]</sup>。该技术能够实现动态聚焦,具有高检测分辨率、高信噪比和高灵敏度等优点。笔者主要讨论相控阵超声成像硬件电路,其中

收稿日期:2013-09-12

基金项目:国家科技部国际合作资助项目(2011DFR71080)

作者简介:王海涛(1968—),男,博士,教授,主要从事光学、超声、电磁无损检测技术的研究。

包括超声发射电路及获取回波信号之后的调理电路,并通过超声标准试块验证设计的硬件电路的可行性。

### 1 发射电路

超声发射电路主要包括电源、驱动电路、发射电路、阻尼电阻和超声探头。发射电路直接影响着超声信号的特性。发射电路采用电容瞬间充放电电路,产生尖脉冲激励信号来激励超声探头<sup>[2]</sup>。根据脉冲激励原理可知,为了更有效地激励超声探头,要尽量减少激励脉冲上升时间,提高激励脉冲幅度,减少脉冲宽度<sup>[3]</sup>。激励脉冲上升时间主要由电路开关的完全闭合速度决定,脉冲幅度和宽度主要受直流高压幅度和开关电路的影响;因此,必须选择合适的

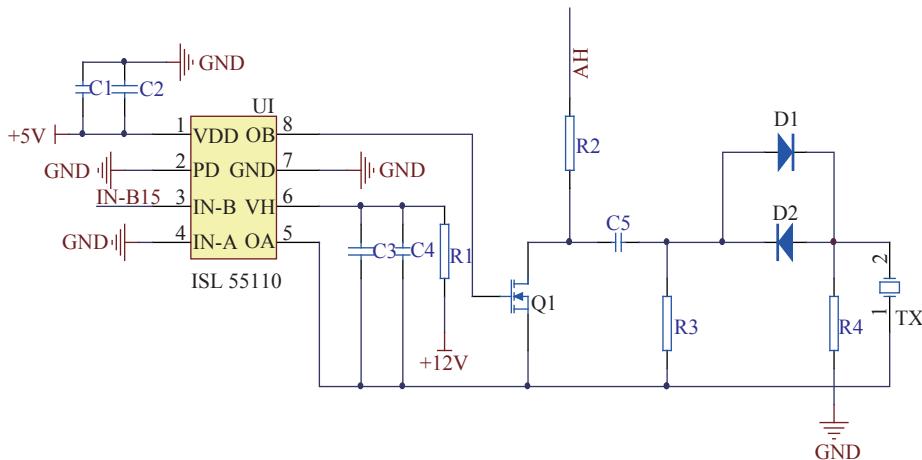

图 1 超声发射电路原理图

开关元件和驱动芯片。

硬件系统的超声发射电路原理图如图 1 所示。驱动电路中驱动芯片使用 ISL55110，并且选择场效应管作为开关元件。ISL5510 可输出 5~12 V 的脉冲电压，具有 1.5 ns 的上升和下降时间，驱动电流可达到 3.5 A，能快速对场效应管的输入电容进行充放电，实现场效应管的高速导通。ISL5510 需要 5,12 V 工作电压，并控制输入电压的上电顺序。为了使芯片稳定工作，在电压输入管脚并联瓷片电容和钽电容对输入电压进行去耦处理，同时在 12 V 电压输入端串联合适的电阻进行限流。

触发脉冲未到来之前，高电压对电容 C5 进行充电；触发脉冲到来之后，高电压对电容 C5 进行放电。二极管 D1 和 D2 在发射激励脉冲时，由于采用正向接法，故不影响 C5 的充放电；而在接收回波时，由于回波信号幅度都是几十微伏数量级，两个二极管均处于截止状态，因此二极管起到隔离作用，消除发射电路对接收电路的影响<sup>[4]</sup>。R4 是阻尼电阻，具有增加探头的阻尼作用；为了使产生的回波信号比较理想，需要选择合适的电阻值。该系统主要实现 16 路相控阵超声检测，将使用带有 16 个阵元的相控阵探头。但在调试单通道电路时，将利用相控阵探头中的一个阵元进行试验。

## 2 信号处理电路

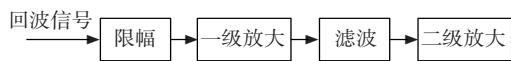

超声换能器直接接收到的超声回波信号，幅度比较高且含有不同频率的杂波，故需要对接收到的超声回波信号进行处理。超声回波信号处理的原理框图如图 2 所示。

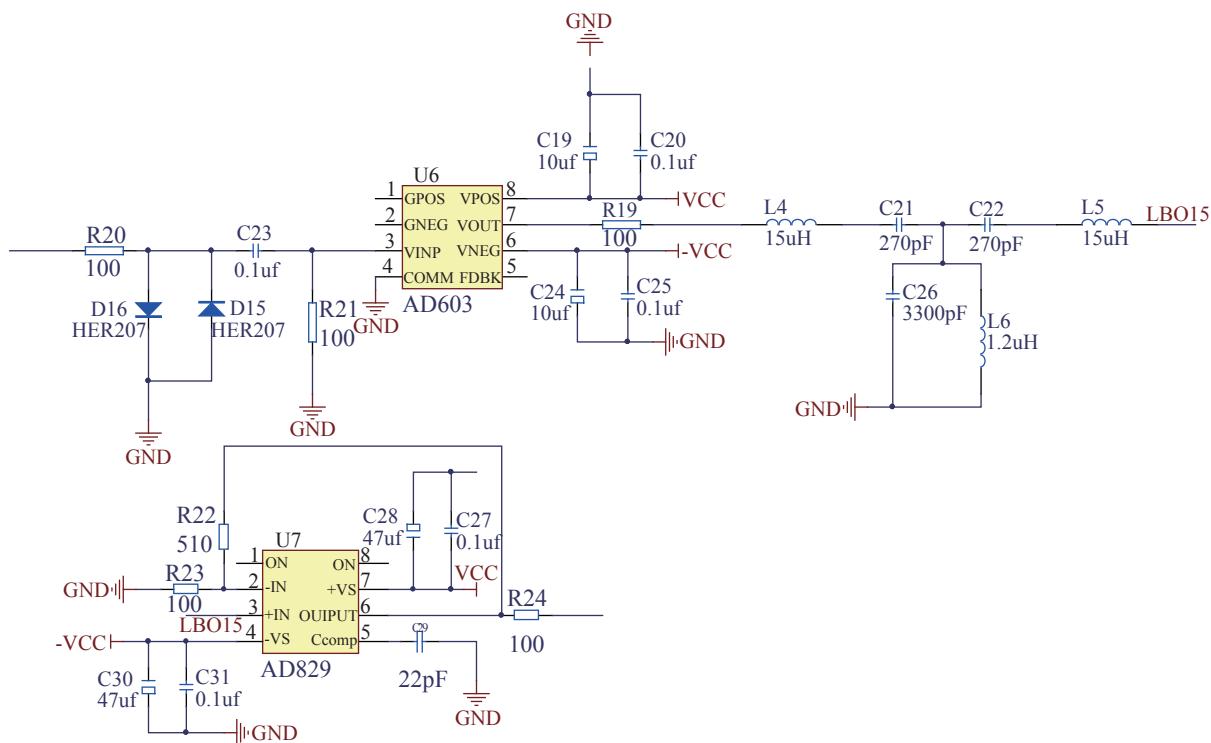

根据这个原理框图，设计相应的信号处理电路，如图 3 所示。

图 2 回波信号处理原理框图

由于接收到的回波信号幅度比较高，如果不对手波信号进行处理就直接送到后级的运放中进行放大，会对运算放大器产生冲击，甚至会损坏放大芯片，使整个系统无法工作。所以，进行信号放大之前需要对信号进行限幅处理，系统中使用二极管钳位电路对回波信号进行限幅处理。为了避免限幅电路受到强电流冲击，在二极管之前串联了限流电阻。系统的放大电路部分分别采用 AD603 和 AD829 进行放大。AD603 是低噪声且由电压控制的增益放大器，AD603 的放大倍数计算公式为  $G_{\text{ain}}(\text{dB}) = 40V_G + G_0$ 。其中  $V_G$  是差动式输入的增益控制电压； $G_0$  根据不同的接法，分别为 10, 20, 30 dB。系统中  $V_G$  为 0,  $G_0$  为 30 dB，所以前级放大的倍数为 30 dB。放大回波信号的同时也放大杂波信号，需要对回波信号进行滤波处理。根据探头的中心频率 4 MHz，设计一个中心频率为 4 MHz，带宽为 1 MHz 的三阶巴特沃斯带通滤波器。使用 Filter Solutions 输入滤波器参数，就可以得到电容电感的数值<sup>[5]</sup>。然后根据市面上有售的电容电感值微调电容电感值，完成滤波器设计。后级使用 AD829 进行放大，AD829 是高速低噪声放大器。由于滤波后的信号相对还是比较微弱，因此在这一级放大部分可以将放大倍数调整为 10，放大之后的信号相对比较理想，有利于之后的软件处理。以上设计的是单通道超声检测电路，多通道超声相控阵检测电路只需根据系统要求对单通道电路进行相应扩展，然后通过 FPGA 来控制触发信号延时，实现延时激励不同

图 3 超声回波信号处理电路

的阵元。

### 3 试验测试

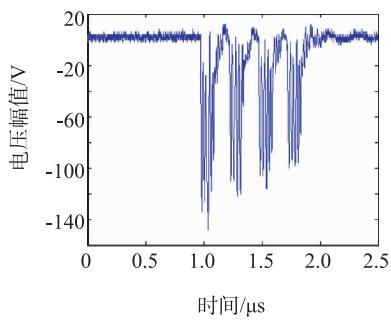

为了验证自行设计的单通道电路的效果,使用超声检测标准铝块进行测试。在 ISL55110 的输入端输入频率为 4 MHz,幅度为 3.3 V,时间间隔为 20 ms 的四个连续触发信号。超声换能器在高压负脉冲的激励下产生超声波,发射电路的作用就是产生高压负脉冲。将 ISL55110 上电工作后,测量超声探头前端的波形,测得的波形如图 4 所示。

图 4 高压负脉冲波形

从图 4 中可以看出,由于输入了连续的四个脉冲信号,后三个脉冲信号逐个衰减。如果只输入一个脉冲信号就不会出现逐个衰减现象。测得第一个脉冲的电压峰值为 145 V,而实际高压端的输入电压为 240 V,衰减将近 40%。出现这种现象,主要是

因为选用的场效应管的开关时间没有达到理想的工作状态,并且场效应管的结电容也会造成电压衰减。同时产生的高压负脉冲也存在一些问题,波形中包含大量的振荡干扰。通过分析,这些振动干扰主要是由于 ISL55110 输入逻辑信号频率偏高,引入振铃,间接导致 MOSFET 的开关效果变差。但是发射电路产生的高压负脉冲,已经达到激励超声换能器工作的要求。然后对超声标准试块进行检测,图 5 显示的是稳压输出之后的信号波形。

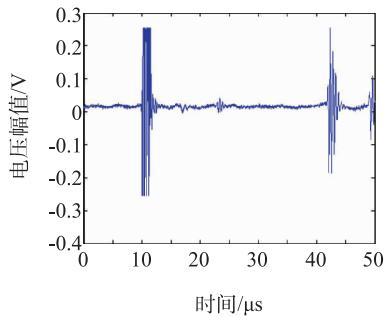

图 5 稳压输出波形

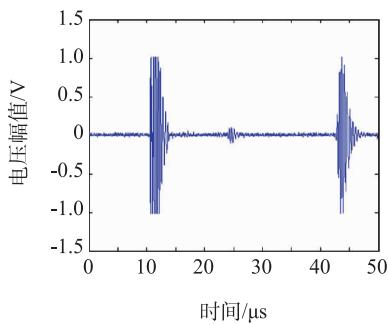

通过图 5 可以看出,稳压之后的缺陷回波的幅值已经稳定在 20 mV 左右,已经能够满足放大芯片的信号输入要求。图 6 显示的是通过带通滤波器之后的回波信号波形,可看出,缺陷回波信号的幅值,经过 AD603 放大之后已经得到明显的放大,并且波形中的杂波信号已经被滤除。

图 6 滤波之后的回波信号

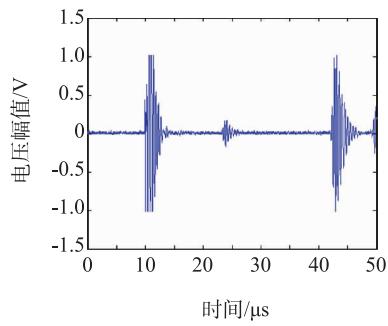

图 7 显示的是回波信号经过 AD829 放大之后的信号,可以看出,缺陷回波的幅值经过两级放大之后,已经达到可分辨的程度,这样的信号波形可通过

图 7 放大之后的缺陷回波信号

(上接第 18 页)

## 2 结论

基于 FPGA 芯片复杂而强大的时序功能,通过锁相环的倍频相移(实现周期 1 ns 的时钟信号)、发射控制电路的流水线设计和等延时实现、逻辑区域的合理约束等,实现了相控阵发射延时的 1 ns 分辨率。Modelsim 软件的仿真结果验证了基于 FPGA 的超声相控阵高精度延时设计的可行性和正确性。

### 参考文献:

- [1] 程继隆. 超声相控阵检测关键技术的研究[D]. 南京:南京航空航天大学, 2010.

- [2] 孙芳. 超声相控阵技术若干关键问题的研究[D]. 天津:天津大学, 2012.

- [3] 鲍晓宇, 施克仁, 陈以方. 超声相控阵系统中相控发射与同步的实现[J]. 无损检测, 2003, 25(10): 507-510.

- [4] 张伟. 相控阵聚焦法则算法实现关键技术研究[D]. 成都:西南交通大学, 2012.

- [5] 杨天雪. 延时分辨率对超声相控阵检测性能的影响[J]. 质量技术监督研究, 2009(6): 15-18.

- [6] 施克仁, 郭寓岷. 相控阵超声成像检测[M]. 北京:高等教育出版社, 2010.

- [7] 冯红亮, 肖定国, 徐春广, 等. 脉冲超声传感器激发/接收电路设计[J]. 仪表技术与传感器, 2003(11): 30-32.

- [8] 游云通, 刘松平, 宋秀荣. 一种新颖的宽窄脉冲超声波发生电路[J]. 航空制造技术, 2004(4): 88-91.

- [9] 龙云玲, 刘艳, 秦鑫, 等. 医用小型 B 超仪发射电路设计[J]. 中国医疗设备, 2011(6): 35-36.

- [10] 吴见平, 周宇, 陈国帅. 利用 Filter Solutions 辅助设计滤波器[J]. 大众科技, 2012(3): 8-10.

- [11] 王冠, 俞一鸣. 面向 CPLD/FPGA 的 Verilog 设计[M]. 北京:机械工业出版社, 2007.

- [12] 万昊, 包斌, 成桂梅. 一种现场可编程门阵列门延时精确调整时序的方法[J]. 航天返回与遥感, 2010(2): 66-72.

- [13] 王诚, 蔡海宁, 吴继华. Altera FPGA/CPLD 设计基础篇[M]. 北京:人民邮电出版社, 2011.

- [14] 李兰英. Nios II 嵌入式软核 SOPC 设计原理及应用[M]. 北京:北京航空航天大学出版社, 2006.

- [15] 刘婧, 靳世久, 陈世利, 等. 高集成度超声相控发射电路的设计[J]. 传感技术学报, 2010(8): 58-62.

- [16] 陈欣波. Altera FPGA 工程师成长手册[M]. 北京:清华大学出版社, 2012.

- [17] 杨斌. 超声相控阵系统中高精度触发系统研究[D]. 太原:中北大学, 2007.

- [18] DAVID R S, PAUL D F. 面向数字系统综合的 Verilog 编码风格[M]. 汤华莲, 田泽, 译. 西安:西安电子科技大学出版社, 2007.

- [19] 王金明. 数字系统设计与 Verilog HDL[M]. 北京:电子工业出版社, 2009.

- [20] 吴继华, 蔡海宁, 王诚. Altera FPGA/CPLD 设计高级篇第 2 版[M]. 北京:人民邮电出版社, 2011.

采集卡采集之后送入计算机,从而进行缺陷的还原。

## 4 结论

通过试验数据可以看出,超声发射接收电路能够实现对于缺陷的检测。这样,设计一个多通道的超声相控阵检测装置,只需要将单通道超声检测电路根据需求相应扩展,并通过 FPGA 控制阵列探头中各个阵元激励脉冲的时间延迟,实现聚焦点位置和声束方位的变化,从而合成相控波束,完成超声扫描成像。将 FPGA 和此系统组合起来可得到一个通道超声相控阵检测仪的硬件部分。

### 参考文献: