# 超声相控阵高精度延时设计的 FPGA 实现

杨先明<sup>1</sup>, 王海涛<sup>2</sup>, 赵大丹<sup>2</sup>, 郭瑞鹏<sup>2</sup>, 沈立军<sup>2</sup>

(1. 烟台富润实业有限公司, 烟台 264670; 2. 南京航空航天大学 自动化学院, 南京 210016)

**摘要:**超声相控阵检测是通过控制超声波的相位延时实现声束偏转聚焦, 继而完成探测被测试件内部缺陷的技术, 因此相位延时精度是此技术的关键所在。因现场可编程门阵列(FPGA)芯片具有复杂而强大的时序功能, 故系统的设计基于FPGA芯片, 利用锁相环的倍频和移相技术, 采用同步和等延时设计, 最终实现了1 ns的阵元发射延时精度。同时, 设计使用嵌入式处理器, 实现延时时间、激励信号的周期及重复频率的可重配置功能。Modelsim软件的仿真结果, 验证了设计的可行性和正确性。

**关键词:**相控阵延时; verilog HDL; FPGA; NIOS II 处理器

中图分类号: TG115.28

文献标志码: A

文章编号: 1000-6656(2014)05-0016-03

## Ultrasonic Phased Array High Accuracy Time Delay Design of FPGA Implementation

YANG Xian-ming<sup>1</sup>, WANG Hai-tao<sup>2</sup>, ZHAO Da-dan<sup>2</sup>, GUO Rui-peng<sup>2</sup>, SHEN Li-jun<sup>2</sup>

(1. Yantai Furun Industrial Company with Limited Liability, Yantai 264670, China;

2. School of Automation Engineering, Nanjing University of Aeronautics and Astronautics, Nanjing 210016, China)

**Abstract:** By controlling the phase delay of ultrasound, ultrasonic phased array inspection technology achieves beam deflection and focus, then detects internal defects. So the phase delay accuracy is the key to this technology. The FPGA chip has complex and powerful timing functions and meets ultrasonic phased array delay control needs. Through a phase-locked loop frequency multiplier and phase shift, the system adopts synchronization and latency design, and reaches 1 ns delay resolution. Simultaneously, processor achieves parameters reconfiguration function, and those parameters are the delay time and cycle and repetition frequency of the excitation signal. Modelsim software simulation results verify the feasibility and correctness of the design.

**Keywords:** Ultrasonic phased array; verilog HDL; FPGA; NIOS II processor

超声相控阵检测时, 按照一定的延时规律来顺序激发探头各阵元, 其产生的超声发射子波束在空间合成, 形成波束聚焦、偏转等效果; 当波束遇到目标时产生回波, 通过对回波信号进行延时补偿、加权求和等处理, 最后形成超声成像<sup>[1-2]</sup>。由此可见, 相位延时技术是超声相控阵技术的核心, 是多种相控效果的基础<sup>[3-4]</sup>。延时分辨率(阵元间发射声波的相对最小延时)是超声相控阵实现聚焦效果的关键, 能影响缺陷或者损伤可视化的分辨率和相控阵系统

的检测性能<sup>[5-7]</sup>。

笔者完成了超声相控阵各阵元激励声波的高精度延时设计。系统利用锁相环的倍频和移相技术, 采用同步和等延时设计, 实现1 ns的阵元发射延时精度。同时, 使用嵌入式处理器, 实现延时时间、激励信号的周期及重复频率的可重配置功能, 可满足不同中心频率的超声探头。

### 1 系统设计

#### 1.1 超声相控阵发射电路的设计

该电路设计适用于16阵元的超声探头, 延时分辨率1 ns, 脉冲激励中心频率可控。根据电路设计要求, 系统选择了Altera公司CYCLONE IV系列

收稿日期: 2013-09-12

基金项目: 国家科技部国际合作资助项目(2011DFR71080)

作者简介: 杨先明(1978—), 男, 硕士, 总经理助理, 主要研究方向为超声相控阵无损检测。

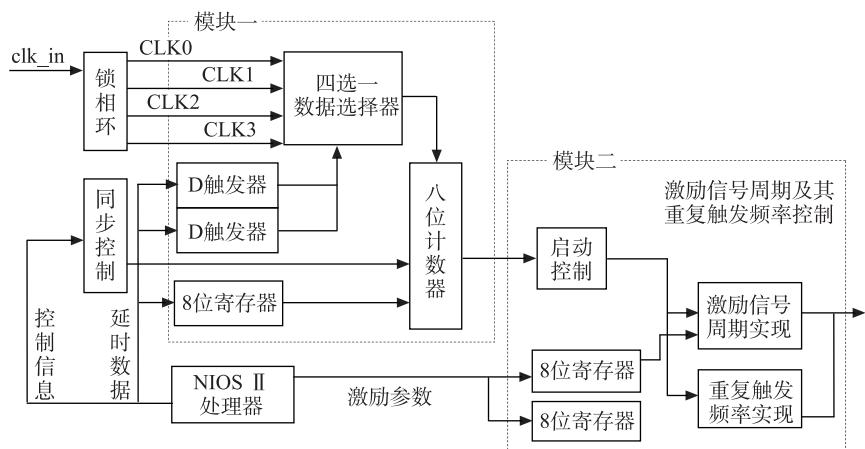

图1 超声相控阵阵元激励原理框图

的FPGA芯片,虽然FPGA芯片pin to pin延时是不可预测的,不像CPLD pin to pin的延时是固定的<sup>[8]</sup>,但是相控阵阵元激励信号控制模块的流水线设计,逻辑锁定区域的合理规划,时序关键路径的优化,可使得各阵元延时激励可控。

超声相控阵阵元激励原理框图(一个通道)如图1所示。嵌入在FPGA器件中的NIOS II处理器<sup>[9]</sup>,首先根据聚焦法则,计算出各个通道的延时时间;接着将延时参数和阵元激励信号的周期以及重复触发频率等参数数据,传送给相控阵阵元激励控制电路,从而确定各个阵元激励的延时时间、激励信号的频率以及重复触发的次数;最后发送启动信号给同步控制电路,同时启动16路通道,激励阵元。

参考图1中的模块一,若将延时发射分为细延时和粗延时,那么锁相环、D触发器和数据选择器实现细延时,实现1 ns内的延时分辨率;8 bit寄存器和计数器实现粗延时,是锁相环输出时钟周期的整数倍,粗延时分辨率为4 ns。参考图1中的模块二,8 bit寄存器存储激励参数,内部计数器时钟周期是4 ns,则激励信号周期的范围为490.196 kHz~125 MHz,而现今超声检查领域中,探头的中心谐振频率范围为1.0~12.0 MHz,电路远远超出了目前所有超声探头的使用需求。超声波在介质中传播时,随着传播距离的增加,由于散射、声束扩散和介质吸收等因素的影响,其能量会逐渐减弱;为了加强超声波聚焦能量,设计了重复触发频率,控制每次各个阵元延时激励的重复次数。

## 1.2 系统时钟设计

锁相环一般用于同步时钟输入和时钟综合,包括分频、倍频、移相等操作<sup>[10~11]</sup>。FPGA芯片晶振频率为50 MHz,采用锁相环的移相和倍频,实现

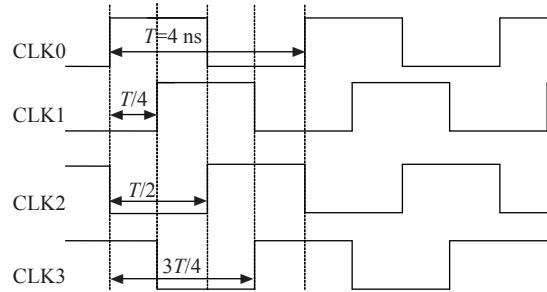

250 MHz时钟输出,4个输出时钟依次相移90°。输出时钟信号周期4 ns,在4个信号中,每隔1 ns便有一个上升沿,如图2所示。锁相环的4个输出时钟作为数据选择器的数据端,细延时作为数据选择器的地址选择信号,决定数据选择器的输出,即计数器的时钟信号。如此,系统粗细延时相结合,实现了时钟精度1 ns的细延时控制。

图2 锁相环输出时钟信号示意图

## 1.3 系统同步设计

根据波动声学理论,形成稳定的叠加干涉效应有两个条件:一是频率相同,二是相位差恒定,即相干波条件。因此,系统设计必须保证:一方面,超声相控阵探头所有阵元的激励信号频率相同;另一方面,为了实现各通道间相位差恒定,在超声发射过程中,必须使各通道激励脉冲按照系统设置的延时量延时,即必须实现各个通道计数延时的同步性和一致性,激励的脉冲信号才能满足相干条件而形成干涉叠加,从而达到高精度延时发射的目的<sup>[12~13]</sup>。

全局时钟是保证各个通道相位差恒定的前提。整个系统的时钟均是来自一个锁相环的输出,这首先保证了所有时钟信号的零相位差。系统设计同步控制,保证了16通道同时启动计数延时。因为所有的设计最终实现在于FPGA芯片上的逻辑阵列模

块(Logic Array Block, LAB), LAB 之间信息传递的布线,必然会产生延时,时钟信号和同步信号必须同时到达 16 个通道,那么必须进行逻辑区域约束,布线合理规划,以达到等延时启动的目的。

### 1.4 阵元延时激励功能实现

相控阵阵元激励控制电路,包括同步控制、延时控制、激励信号周期及重复触发频率控制,是采用 Verilog HDL 编写来实现的,其设计思想是自顶而下,实现则是自底而上<sup>[14]</sup>。自顶而下的设计是指将一个大规模的数字电路系统从功能上化为若干个不相干的模块,每个子模块又可以根据功能需要化为若干个二级子模块,以此类推,直至功能模块小到比较容易实现为止。这里的不相干是指同级别的子模块之间功能完全独立而不相互依赖,但并不是模块之间不可通讯,实际设计中,模块之间的通讯非常重要。

即使实现同一逻辑功能,Verilog 编写的程序不同,综合成的 RTL 级原理图也不相同,那么物理资源分配肯定不一样,最终实现的时序功能也可能相差甚大。设计自定义了数据选择器的编写,而没有使用传统的编程方法。自定义数据选择器保证了地址端信息等延时的传递,数据端 4 个输入具有相同的逻辑资源布局布线,可实现等延时的时序功能,而传统的数据选择器不能形成等同的布局布线,降低了延时精度。通过观察 FPGA 芯片的资源分配,等延时的设计得以验证。

图 1 中模块一和模块二都使用了 D 触发器和寄存器,用于暂存延时数据参数,这是 verilog HDL 的典型流水线设计。流水线是指在多级组合逻辑中间插入寄存器,暂存中间结果以缩短延时。延时时间、激励信号的周期及重复频率等数据的路径走线延时,包括寄存器到组合逻辑的线延时、组合逻辑内部逻辑门之间的线延时和通过逻辑门的时间,直接影响后级激励信号的延时精度,流水线是缩短此延时的一种有效手段,进而可改善电路性能<sup>[6]</sup>。

影响延时分辨率的因素,除了激励电路设计能够达到的相对延时,整个设计在 FPGA 芯片上的模块之间的布局布线,也会造成物理延时。直接影响布局布线结果的因素是电路设计的工程综合,综合是指在不改变逻辑功能的前提下,根据节省面积、提高速度的原则,将设计的 HDL 程序翻译为最基本的与、或、非门以及 RAM、触发器等基本逻辑单元的连接关系,并根据约束条件优化所生成的门级逻辑连接<sup>[8,15]</sup>。布局布线将综合的逻辑连接与 FPGA

芯片的可用资源进行匹配<sup>[12]</sup>,若对设计的综合过程和布局布线不加约束,则逻辑分布较散,布线较长,导致物理延迟较大,且不可预知。遵守资源走线最短和等延时原则,对各级各个设计模块进行逻辑区域约束,最终达到各通道间等延时的目的。

### 1.5 ModelSim 仿真测试

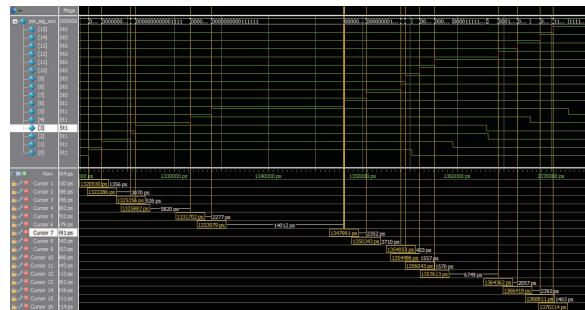

为了验证电路的行为和设计目标是否一致,对其采用 ModelSim 软件进行了仿真测试,相控阵激励电路仿真如图 3 所示。16 通道全部导通,激励信号周期 64 ns,重复触发频率 2,各个通道设置延时时间、相对延时等参数如表 1 所示。结合仿真结果,观察分析表 1 数据可知,16 通道的绝对误差均小于 1 ns,设计达到了 1 ns 的高精度阵元延时激励,系统设计目标实现。

图 3 相控阵阵元激励 modelsim 仿真波形

表 1 相控阵激励延时数据表

ns

| 通道 | 设置延时 | 设置相对延时 | 实测相对延时 | 绝对误差   |

|----|------|--------|--------|--------|

| 0  | 5    | 0      | 0      | 0      |

| 1  | 6    | 1      | 1.356  | 0.356  |

| 2  | 9    | 3      | 3.070  | 0.070  |

| 3  | 10   | 1      | 0.526  | -0.474 |

| 4  | 16   | 6      | 5.820  | -0.180 |

| 5  | 18   | 2      | 2.277  | 0.277  |

| 6  | 32   | 14     | 14.012 | 0.012  |

| 7  | 34   | 2      | 2.352  | 0.352  |

| 8  | 38   | 4      | 3.710  | -0.290 |

| 9  | 38   | 0      | 0.433  | 0.433  |

| 10 | 40   | 2      | 1.557  | -0.443 |

| 11 | 42   | 2      | 1.570  | -0.430 |

| 12 | 48   | 6      | 6.749  | 0.749  |

| 13 | 50   | 2      | 2.057  | 0.057  |

| 14 | 53   | 3      | 2.392  | -0.608 |

| 15 | 54   | 1      | 1.403  | 0.403  |

(下转第 22 页)

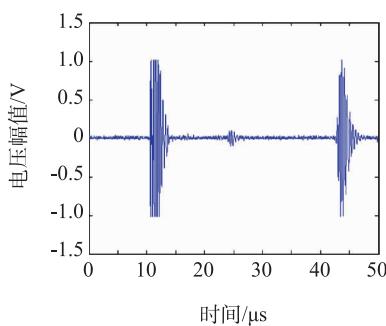

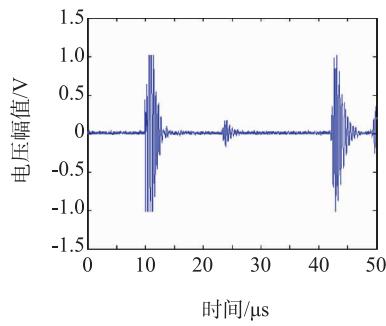

图 6 滤波之后的回波信号

图 7 显示的是回波信号经过 AD829 放大之后的信号,可以看出,缺陷回波的幅值经过两级放大之后,已经达到可分辨的程度,这样的信号波形可通过

图 7 放大之后的缺陷回波信号

(上接第 18 页)

## 2 结论

基于 FPGA 芯片复杂而强大的时序功能,通过锁相环的倍频相移(实现周期 1 ns 的时钟信号)、发射控制电路的流水线设计和等延时实现、逻辑区域的合理约束等,实现了相控阵发射延时的 1 ns 分辨率。Modelsim 软件的仿真结果验证了基于 FPGA 的超声相控阵高精度延时设计的可行性和正确性。

### 参考文献:

- [1] 程继隆. 超声相控阵检测关键技术的研究[D]. 南京:南京航空航天大学, 2010.

- [2] 孙芳. 超声相控阵技术若干关键问题的研究[D]. 天津:天津大学, 2012.

- [3] 鲍晓宇, 施克仁, 陈以方. 超声相控阵系统中相控发射与同步的实现[J]. 无损检测, 2003, 25(10): 507-510.

- [4] 张伟. 相控阵聚焦法则算法实现关键技术研究[D]. 成都:西南交通大学, 2012.

- [5] 杨天雪. 延时分辨率对超声相控阵检测性能的影响[J]. 质量技术监督研究, 2009(6): 15-18.

- [6] 施克仁, 郭寓岷. 相控阵超声成像检测[M]. 北京:高等教育出版社, 2010.

- [7] 冯红亮, 肖定国, 徐春广, 等. 脉冲超声传感器激发/接收电路设计[J]. 仪表技术与传感器, 2003(11): 30-32.

- [8] 游云通, 刘松平, 宋秀荣. 一种新颖的宽窄脉冲超声波发生电路[J]. 航空制造技术, 2004(4): 88-91.

- [9] 龙云玲, 刘艳, 秦鑫, 等. 医用小型 B 超仪发射电路设计[J]. 中国医疗设备, 2011(6): 35-36.

- [10] 吴见平, 周宇, 陈国帅. 利用 Filter Solutions 辅助设计滤波器[J]. 大众科技, 2012(3): 8-10.

- [11] 王冠, 俞一鸣. 面向 CPLD/FPGA 的 Verilog 设计[M]. 北京:机械工业出版社, 2007.

- [12] 万昊, 包斌, 成桂梅. 一种现场可编程门阵列门延时精确调整时序的方法[J]. 航天返回与遥感, 2010(2): 66-72.

- [13] 王诚, 蔡海宁, 吴继华. Altera FPGA/CPLD 设计基础篇[M]. 北京:人民邮电出版社, 2011.

- [14] 李兰英. Nios II 嵌入式软核 SOPC 设计原理及应用[M]. 北京:北京航空航天大学出版社, 2006.

- [15] 刘婧, 靳世久, 陈世利, 等. 高集成度超声相控发射电路的设计[J]. 传感技术学报, 2010(8): 58-62.

- [16] 陈欣波. Altera FPGA 工程师成长手册[M]. 北京:清华大学出版社, 2012.

- [17] 杨斌. 超声相控阵系统中高精度触发系统研究[D]. 太原:中北大学, 2007.

- [18] DAVID R S, PAUL D F. 面向数字系统综合的 Verilog 编码风格[M]. 汤华莲, 田泽, 译. 西安:西安电子科技大学出版社, 2007.

- [19] 王金明. 数字系统设计与 Verilog HDL[M]. 北京:电子工业出版社, 2009.

- [20] 吴继华, 蔡海宁, 王诚. Altera FPGA/CPLD 设计高级篇第 2 版[M]. 北京:人民邮电出版社, 2011.

采集卡采集之后送入计算机,从而进行缺陷的还原。

## 4 结论

通过试验数据可以看出,超声发射接收电路能够实现对于缺陷的检测。这样,设计一个多通道的超声相控阵检测装置,只需要将单通道超声检测电路根据需求相应扩展,并通过 FPGA 控制阵列探头中各个阵元激励脉冲的时间延迟,实现聚焦点位置和声束方位的变化,从而合成相控波束,完成超声扫描成像。将 FPGA 和此系统组合起来可得到一个多通道超声相控阵检测仪的硬件部分。

### 参考文献: