DOI: 10.11973/wsjc240511

# 基于声学显微 C 扫描检测技术的倒装集成电路失效分析

李登科, 王高凯

(中国空空导弹研究院, 洛阳 471009)

**摘要:** 随着倒装集成电路在电子产品中的广泛应用及其失效问题的日益凸显, 对其失效分析技术的要求越来越高。研究了声学显微镜C扫描模式下换能器频率、放大器增益和倒装集成电路芯片厚度间的关系, 发现声学扫描图像清晰度随着换能器频率的增加而提升; 相同频率下, 芯片厚度增加时, 需提高放大器的增益来保证成像质量。此外还研究了声学显微C扫描检测技术在倒装集成电路失效分析中的应用场景, 结果表明该技术可以无损检测出倒装集成电路内部的空洞、分层及裂纹等缺陷, 完成对失效机理的准确判断。

**关键词:** 声学扫描显微镜; 倒装芯片; 失效分析; 分层; 芯片裂纹

中图分类号: TN407; TG115.28

文献标志码: A

文章编号: 1000-6656(2025)02-0001-06

## Failure analysis of flip integrated circuits based on acoustic microscopy C-scan detection technology

LI Dengke, WANG Gaokai

(China Airborne Missile Academy, Luoyang 471009, China)

**Abstract:** With the widespread application of flip-chip integrated circuits in electronic products and the increasingly prominent issue of their failures, the requirements for their failure analysis technology have become increasingly demanding. The relationship among the transducer frequency, amplifier gain, and integrated circuits flip-chip thickness in C-scan mode of the acoustic microscope was explored. It was found that the clarity of ultrasonic scanning images was effectively improved with the increase in transducer frequency; at the same frequency, as the chip thickness increased, the gain of the amplifier was needed to be increased to ensure imaging quality. Furthermore, the application scenarios of acoustic microscopic C-scan detection technology in the failure analysis of flip-chip integrated circuits were investigated. The results indicated that this technology can nondestructively detect defects such as voids, delamination, and cracks inside flip-chip devices, enabling accurate judgment of failure mechanisms.

**Key words:** scanning acoustic microscope; flip chip; failure analysis; delamination; chip crack

集成电路产业逐步进入后摩尔时代, 通过降低半导体器件的特征尺寸来提高其性能的发展路径受到了极大的影响, 人们开始探索半导体技术的全段工艺系统级创新<sup>[1]</sup>。封装技术是集成电路产业中极为重要的一个环节, 开始受到越来越多的关注。倒

装芯片封装是一种先进的封装技术, 可以减少芯片互联工艺中对引线的限制, 有效降低互联线引入的信号延迟和寄生效应, 极大提升微电子器件输入/输出(I/O)的密度和效率, 已经被广泛应用于各类微电子器件的封装<sup>[2-3]</sup>。随着人们对算力需求的不断提升, 超大规模集成电路已经广泛应用于各类电子产品中, 由于倒装集成电路结构和工艺的特殊性, 此类集成电路常面临各种潜在的失效风险, 因此对超大规模倒装集成电路的失效分析具有重要意义<sup>[4]</sup>。

收稿日期: 2024-10-29

作者简介: 李登科(1979—), 男, 硕士, 高级工程师, 主要从事集成电路无损检测方向的研究工作

通信作者: 王高凯, 1352457297@qq.com

声学扫描技术是一种方便快捷的表征手段,在微电子器件的失效分析中具有广泛的应用。文章基于倒装集成电路,研究了声学扫描显微镜C扫描检测技术的换能器频率、放大器增益和芯片厚度三者间的关系以及倒装集成电路常见的失效模式,并为倒装集成电路的选用标准提出了合理化建议。

## 1 倒装集成电路与声学扫描技术

### 1.1 倒装集成电路

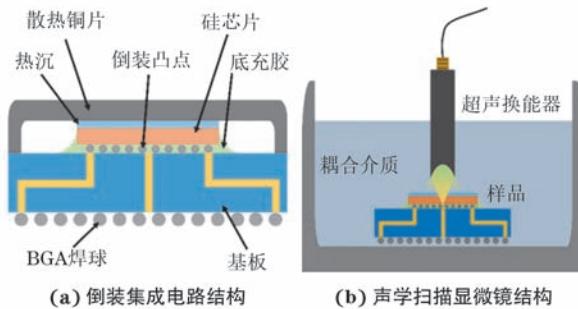

倒装集成电路典型结构如图1(a)所示,从上到下依次为散热金属、热沉、芯片、底充胶和基板;图1(b)为声学扫描显微镜结构示意。正面植有凸点焊球的芯片倒扣在基板上,通过焊接工艺将芯片与基板相连<sup>[5]</sup>。由于芯片与基板的热膨胀系数(CTE)

图1 倒装集成电路和声学扫描显微镜结构示意

相差较大,器件受到热应力时,芯片与基板的连接处可能会出现断裂,引发器件功能失效。为了解决热膨胀系数不匹配的问题,通常会在芯片和基板之间注入一层底充胶作为缓冲层。研究表明,底充胶可以有效提升焊点热疲劳寿命,保证器件的可靠性<sup>[6]</sup>。

底充胶的填充过程主要利用了液体的毛细现象,在完成焊接的芯片一侧滴注适量含有SiO<sub>2</sub>颗粒的环氧树脂,流动液体在表面张力的作用下,沿着芯片和基板的表面逐渐对二者间的空隙进行充分填充,待环氧树脂完全固化后在芯片和基板之间形成了底充胶。随着芯片尺寸的增大,底充胶填充过程中不可避免地会出现空洞和分层,进而引起焊点失效,影响倒装器件的性能,因此,目前对于大规模倒装集成电路的失效分析主要围绕底充胶相关的缺陷展开。

### 1.2 声学扫描技术

声学扫描技术属于无损检测技术的一种,可以实现器件内部微小缺陷的快速无损检测<sup>[7]</sup>。声学扫描技术与常用无损检测技术的特性对比如表1所示,可见声学扫描技术具有非接触性、非破坏性、穿透力强以及对微小缺陷的检测灵敏度高等特点,因此文章主要采用声学扫描技术对倒装集成电路开展失效分析。

表1 声学扫描技术与常用无损检测技术的特性对比

| 项目     | 技术类型       |                 |                  |                  |

|--------|------------|-----------------|------------------|------------------|

|        | 声学扫描技术     | X射线检测           | 涡流检测             | 渗透检测             |

| 非接触性   | 是          | 是               | 否(需接触导电材料)       | 否(需接触材料表面)       |

| 穿透力    | 强(适用于多层结构) | 强(适用于较厚材料)      | 中等(限于导电材料表面和近表面) | 弱(限于表面开口缺陷)      |

| 微小缺陷检测 | 高灵敏度       | 高灵敏度(受材料密度差异影响) | 中等灵敏度            | 较低灵敏度(对内部缺陷无法判定) |

| 实时成像   | 是          | 是               | 否                | 否                |

| 安全性    | 对人体无害      | 对人体有电离辐射危害      | 对人体无害            | 部分材料可能对人体有害      |

| 检测速度   | 快(可自动化扫描)  | 快(受成像速度影响)      | 快(需专业人员分析)       | 快(需人工操作和观察)      |

声学扫描技术主要利用不同介质的声阻差异来鉴别材料中可能存在的缺陷,是一种常用的元器件无损检测手段。其使用声学扫描显微镜[见图1(b)]进行检测,检测时将去除了散热铜片的器件浸没到耦合介质中(通常为去离子水),换能器周期性地发射和接收超声波对样品进行扫描。C扫描是声学显微技术的一种工作模式,该模式需要选择某段超声信号作为时间窗口,探测时间窗口内的声波信号并对整个样品进行x-y方向的平面扫描,最后通过信号处理系统形成该平面的二维灰度图像。声学显微C扫描检测技术的成像原理是利用超声波在不同声阻材料界面处

的反射差异,检测某一声学剖面内样品的声阻变化,进而得到样品内部结构的衬度图。此外,由于相比于其他材料,空气的声阻近似为0,故声学显微C扫描检测技术对于孔隙类缺陷十分敏感,可以快速检测出器件中的细小空洞和裂纹等缺陷,在孔隙类缺陷样品的检测和失效分析过程中具有广泛的应用前景<sup>[8]</sup>。

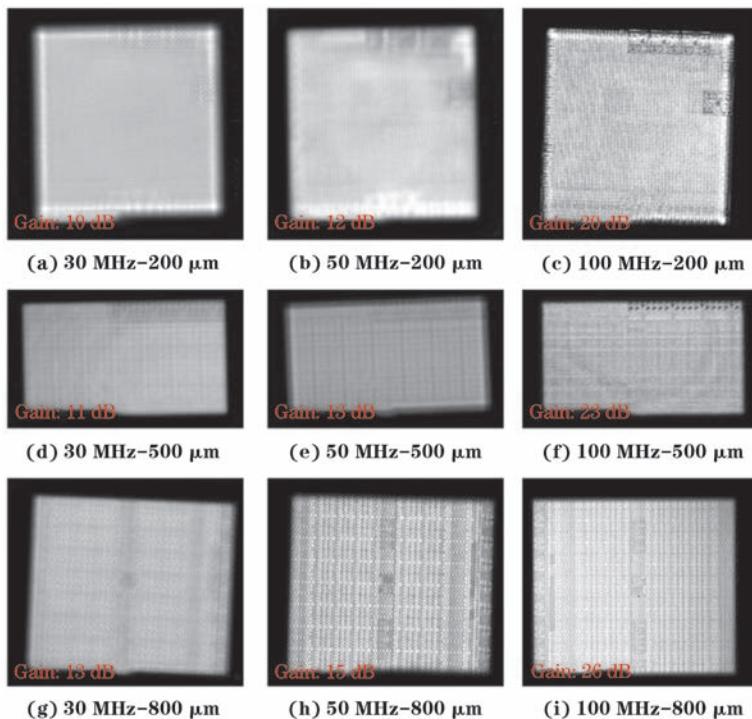

不同换能器可以产生不同频率的超声波,通常超声波的频率越高,波长越短,最终得到的图像分辨率越高。常用的换能器超声频率包括30, 50, 100 MHz, 其中30 MHz换能器的焦距为13 mm, 轴向分辨率为50 μm, 横向分辨率为16.5 μm; 50 MHz

换能器的焦距为 12 mm, 轴向分辨率为 30  $\mu\text{m}$ , 横向分辨率为 10  $\mu\text{m}$ ; 100 MHz 换能器的焦距为 8 mm, 轴向分辨率为 15  $\mu\text{m}$ , 横向分辨率为 5  $\mu\text{m}$ 。不同厚度(200, 500, 800  $\mu\text{m}$ )的芯片在不同频率换能器下的声学扫描图像如图 2 所示, 其扫描范围(长  $\times$  宽, 下同)分别为 15 mm  $\times$  15 mm, 20 mm  $\times$  15 mm 和 20 mm  $\times$  20 mm, 不同扫描频率对应的放大器增益已在图中标出。由图 2 可以发现, 随着换能器频率的提

高, 器件声扫图像清晰度明显提升; 相同频率下, 芯片厚度增加时, 需提高放大器的增益来保证成像质量; 同一厚度的芯片, 随着频率的增加, 换能器的焦距和景深相应缩短, 如果器件的待测范围较大会导致成像不完全, 而且高频声波传输中的衰减程度更大, 为了保证图片成像效果同样需要提高放大器增益。因此, 在用声学扫描显微镜对元器件进行失效分析时, 应选择合适的换能器频率以保证成像质量。

图 2 不同厚度的芯片在不同频率换能器下的声学扫描图像

## 2 倒装集成电路失效分析

笔者以某型超大规模倒装集成电路为例, 研究了声学扫描技术在倒装集成电路失效分析中的应用。

### 2.1 底充胶分层

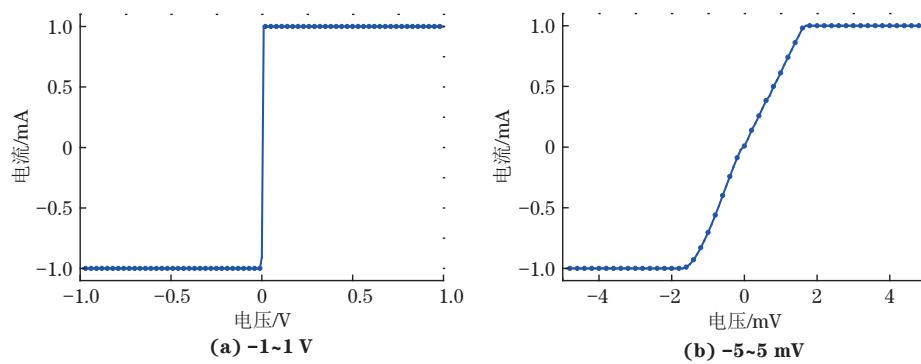

某型倒装集成电路装配至电路板后, 在板测试时发现其供电引脚 V<sub>CCINT</sub> 对地短路, 将器件从电路板上拆下后使用 Keithley 4200-SCS 型源表对其供电引脚和地线进行测试, 不同电压范围内器件 V<sub>CCINT</sub> 与地的电流-电压曲线如图 3 所示。测试电压为 -1~1 V, 步长为 0.01 V, 限制电流为 1 mA, 测试结果如图 3(a) 所示, 可以发现除了在零点附近, 供电引脚对地电流大小基本维持在限制电流左右, 疑似为短路现象; 进一步减小电压测试范围至 -5~5 mV, 步长改为 0.1 mV, 限制电流为 1 mA, 测试结果如图 3(b) 所示, 可以发现器件供电

引脚对地电压在 -1.6~1.6 mV 间呈现典型的电阻特性, 通过计算可得其电阻约为 1.6  $\Omega$ , 表明供电引脚对地呈现短路状态。

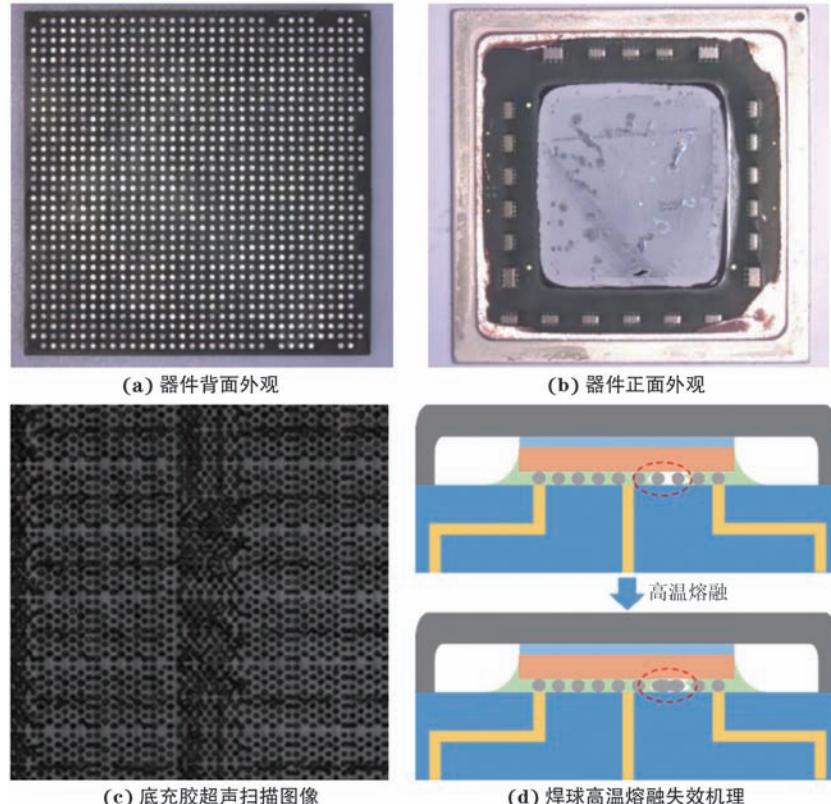

器件外观、超声扫描图像及失效机理如图 4 所示。由器件的背面外观可以发现 BGA 焊球分布均匀, 未出现明显的黏连现象, 初步排除外焊点熔融短接造成短路的可能。为了进一步确定该器件的失效机理, 首先去除其表面的散热金属盖板。图 4(b) 为去除盖板后器件的正面外观图, 发现芯片表面涂有一层灰白色的热沉。为消除热沉的影响, 使用有机清洗剂将芯片表面的热沉去除后再进行后续测试。芯片下的底充胶层缺陷是引起器件功能失效的一个重要因素<sup>[9-10]</sup>, 为了分析器件的失效原因, 使用声学 C 扫描技术进行检测, 扫描对象为芯片下的底充胶层, 换能器频率为 50 MHz, 扫描范围为 20 mm  $\times$  20 mm, 放大器增益为 15 dB, 得到的扫描

图3 不同电压范围内器件  $V_{CCINT}$  与地的电流 - 电压曲线

图4 器件外观、超声扫描图像及失效机理

图像如图4(c)所示,可以发现底充胶与基板存在明显的分层。在器件焊接过程中,当焊接温度高于芯片下方凸点焊球的熔点时,焊球会变为熔融状态,若底充胶存在分层,熔融态的焊球会顺着分层孔隙漫延,其原理如图4(d)所示。

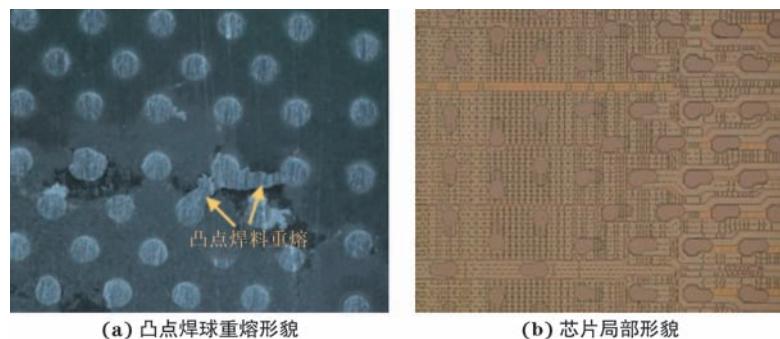

为了检测该器件凸点处是否存在异常,通过机械研磨的方式将器件逐层研磨至芯片下凸点焊球的位置,形貌如图5(a)所示,可见相邻的凸点焊球间存在明显的熔融黏连。为了验证芯片本身是否存在异常,通过化学开封的方法对器件进行开封。芯片形貌如图5(b)所示,检查发现芯片表面无明显的缺陷或过电应力损伤痕迹。综合上述分析结果可知,

芯片下方底充胶存在分层,造成焊接中凸点焊球熔融黏连,导致引脚发生短路。文章使用声学扫描技术,快速确定了底充胶存在的缺陷,明确了失效分析的方向,极大提升了产品故障排除效率。

## 2.2 芯片机械损伤

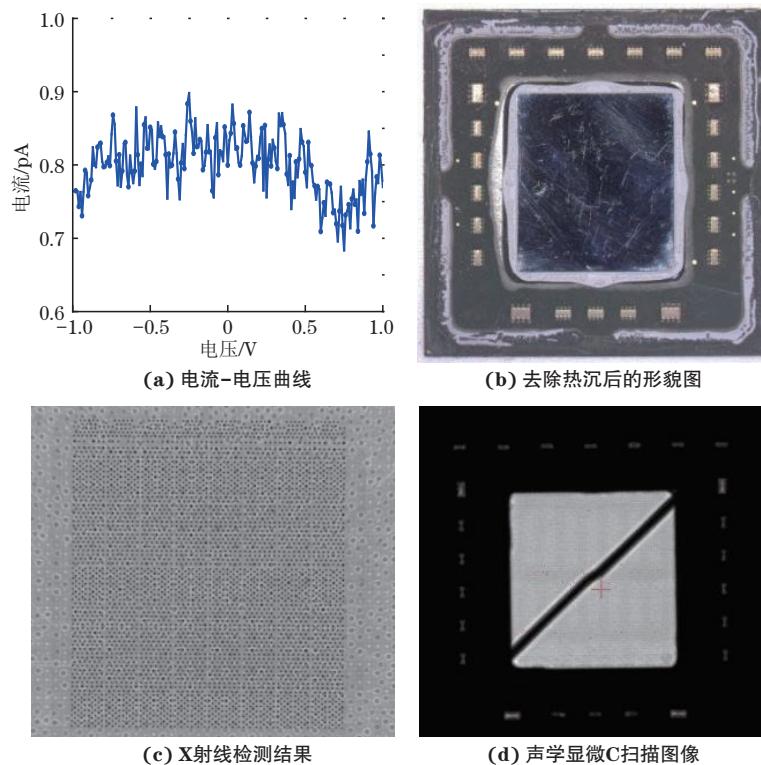

由于芯片、凸点焊料和基板的热膨胀系数不同,热应力引起的芯片机械损伤也是倒装芯片的常见问题,这类损伤通常表现为芯片内部的裂纹缺陷。某型倒装集成电路装配至电路板后,在板测试时发现多路输入对地开路,将器件拆下使用Keithley 4200-SCS型源表对其中一组输入异常电路进行测试,测试电压为-1~1 V,步长为0.01 V,限制电流为

图 5 芯片凸点焊球重熔微观形貌与芯片局部形貌

1 mA, 测试得到的电流-电压曲线如图6(a)所示, 可见除了0.1 pA量级的背景噪声外没有检测到明显的电流, 该曲线属于典型的开路电流-电压特性曲线。

为了探究引起器件输入对地开路的原因, 将器件的金属盖板和热沉去除, 发现其外观形貌未见明显异常[见图6(b)]。使用X射线对器件的结构进行检测, 测试结果如图6(c)所示, 器件的基板及芯片内部结构未见明显缺陷。大尺寸芯片通常存在较大的应力, 应力导致芯片内部出现细微裂纹也是倒装芯片常见的失效模式, 为进一步确定器件的失效机理, 使用声学显微C扫描技术对其进行检测分析, 声扫频率为30 MHz, 扫描范围为30 mm×30 mm, 放

大器增益为13 dB。声学显微C扫描结果如图6(d)所示, 可见芯片内部存在明显的贯穿裂纹, 此裂纹出现在芯片内部且相对较窄, 故光学显微镜和X射线未能检测到此裂纹缺陷, 但超声波在不同介质的界面处会发生强烈干涉, 声学扫描技术对孔隙的检测灵敏度极高, 可以探测到芯片内部的细小裂纹。综合上述测试结果, 推断器件的多路输入异常是由芯片裂纹引起的, 进一步核查发现该器件的焊接温度偏高, 热失配产生的应力使芯片出现了贯穿裂纹, 最终导致器件多路输入对地开路。后续通过调整器件装配工艺和焊接温度, 有效杜绝了此类失效的发生。

图 6 失效器件的电流-电压曲线、去除热沉后的形貌图、X射线检测结果和声学显微C扫图像

### 3 结论

选取某型倒装集成电路为对象,利用声学显微C扫描技术对其失效机理进行了深入分析,得出以下结论。

(1) 声学显微C扫描图像清晰度随着换能器频率的增加而提升;相同频率下,芯片厚度增加时,需提高放大器的增益来保证成像质量;相同厚度的芯片随着换能器频率的增加,同样需要提高放大器增益来确保图像质量。

(2) 声学扫描技术可以无损检测出倒装集成电路内部的空洞、分层及裂纹等缺陷,准确快速地定位和分析失效原因;该技术可为倒装集成电路的质量控制和可靠性评估提供有力的技术支撑。

### 参考文献:

- [1] 张思勉, 邓晓楠, 王宇祺, 等. 后摩尔时代芯片互连新材料及工艺革新 [J]. 中国科学(化学), 2023, 53(10): 2027-2067.

- [2] KIM G, SON K, LEE J H, et al. Size effect on the electromigration characteristics of flip chip Pb-free solder bumps [J]. Electronic Materials Letters, 2022, 18(5): 431-439.

- [3] MIKI T, NAGATA M, SONODA H, et al. Si-backside protection circuits against physical security attacks on flip-chip devices [J]. IEEE Journal of Solid-State Circuits, 2020, 55(10): 2747-2755.

- [4] 罗建辉. Flip Chip 封装零件组装良率提升方法的研究 [D]. 上海: 上海交通大学, 2017.

- [5] 姬青. 宇航用国产倒装芯片结构分析研究 [D]. 上海: 上海交通大学, 2019.

- [6] 张群. 倒装焊及相关问题的研究 [D]. 上海: 中国科学院上海冶金研究所, 2001.

- [7] 刘雨, 夏张松, 宫兆斌, 等. 复合材料修理区域的超声检测 [J]. 无损检测, 2024, 46(10): 81-87.

- [8] 余晓男. 芯片微缺陷的高频超声检测机理与稀疏诊断方法研究 [D]. 无锡: 江南大学, 2021.

- [9] 金鑫. 倒装芯片封装中底部填充技术的分析与优化 [D]. 南京: 东南大学, 2020.

- [10] NG F C, ABAS A, NASHRUDIN M N, et al. Analytical and numerical analyses of filling progression and void formation in flip-chip underfill encapsulation process [J]. Soldering & Surface Mount Technology, 2022, 34(4): 193-202.